FET được chia ra thành JFET và MOSFET. Trong nội dung bài viết này, tất cả chúng ta sẽ cùng tìm hiểu về JFET là gì? Kết cấu và ký hiệu của JFET cũng như nguyên tắc hoạt động của nó nhé.

JFET là gì?

JFET (Junction Field Effect Transistor) hay còn được gọi là Transistor hiệu ứng trường cổng nối hoặc FET nối. Đây là một loại đơn giản của FET (Transistor hiệu ứng trường). Nó thường được sử dụng làm thành phần chuyển mạch điều khiển và tinh chỉnh điện tử hoặc sử dụng làm thành phần khuếch đại hay làm điện trở điều khiển và tinh chỉnh bởi điện áp trong các mạch điện tử…

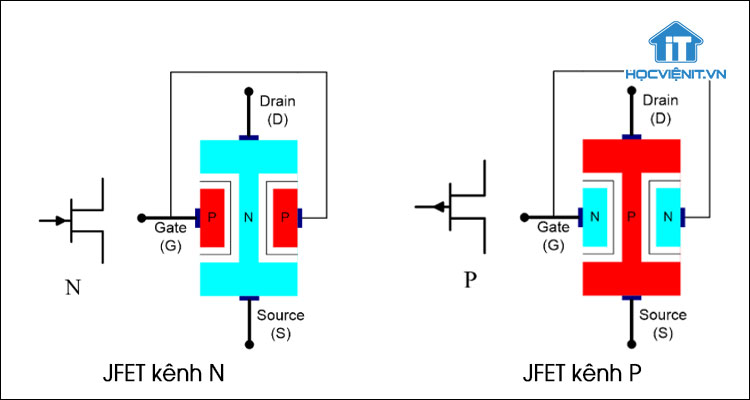

Kết cấu của JFET

Trên một thanh bán dẫn hình trụ có nồng độ tạp chất tương đối lớn (Điện trở suất khá lớn), người ta thiết kế đáy trên và đáy dưới tuần tự được xúc tiếp kim loại để cho ra hai cực tương ứng là cực máng (Cực thoát) và cực nguồn. Tiếp đến, người ta tạo một mối Phường – N vòng theo chu vi của thanh bán dẫn. Kim loại xúc tiếp với mẫu bán dẫn mới, đưa ra ngoài cực cổng (cửa).

Trong số đó:

D (Drain): Cực máng (Cực thoát).

G (Gate): Cực cổng (Cực cửa).

S (Source): Cực nguồn.

– Cực D và cực S được kết nối vào kênh N.

– Cực G được kết nối vào vật liệu bán dẫn Phường.

Thông lộ (kênh) là để chỉ vùng bán dẫn giữa D và S.

Phụ thuộc vào loại bán dẫn giữa D và S mà người ta chia JFET ra thành JFET kênh N và JFET kênh Phường (JFET kênh N thường thông dụng hơn).

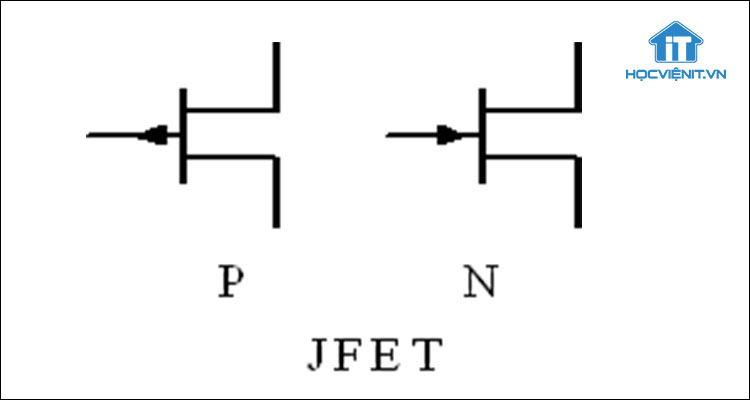

Ký hiệu của JFET

Nguyên tắc hoạt động của JFET

Trước hết, ta đặt một điện áp VDS vào giữa D và S. Khi đó, nó sẽ tạo ra một điện trường tác dụng lên hạt tải phần nhiều của kênh bán dẫn làm chúng chạy từ S sang D và hình thành dòng điện ID. Sau đó, dòng điện ID sẽ tăng theo điện áp VDS cho tới lúc đạt giá trị bão hòa IDSS với mức điện áp được gọi là điện áp thắt kênh VPO, tăng VDS to hơn VPO thì ID vẫn không tăng.

Tiếp theo, ta đặt một điện áp VGS vào giữa G và S sao cho không phân cực hoặc phân cực nghịch mối Phường – N. Trong trường hợp mối Phường – N không phân cực thì ta có dòng ID đạt giá trị lớn số 1 IDSS. Còn so với trường hợp điện áp phân cực nghịch càng lớn thì vùng xúc tiếp (Vùng hiếm) càng mở rộng ra. Việc này khiến tiết diện của kênh dẫn bị thu hẹp lại. Kết quả là lúc điện trở kênh tăng lên thì dòng điện qua kênh ID giảm xuống và trái lại, VGS tăng đến giá trị VPO thì ID giảm về 0.

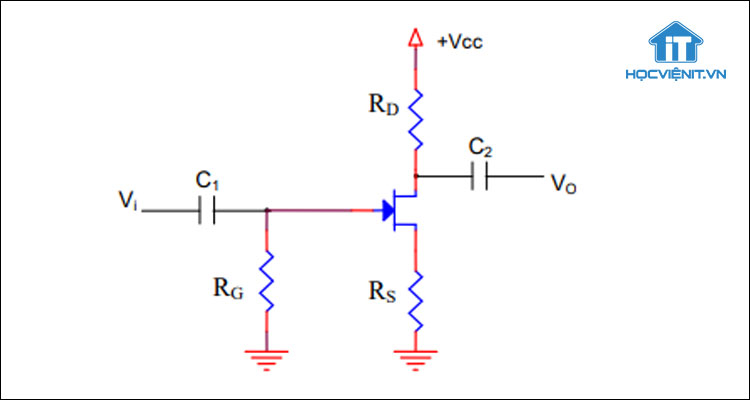

3 cách mắc cơ bản của JFET

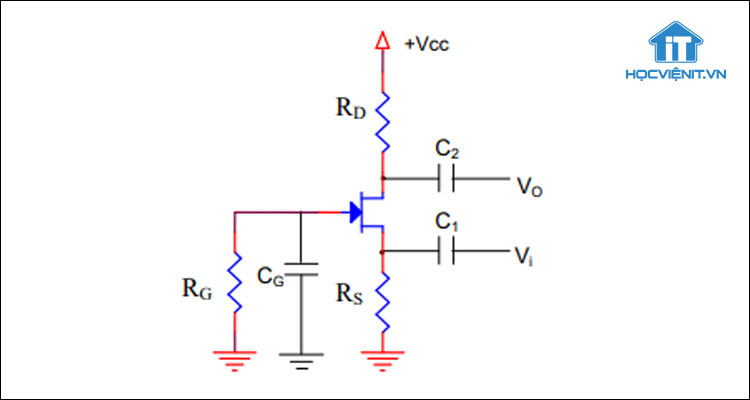

JFET mắc kiểu cực nguồn chung (Common Source = CS)

Tín hiệu vào G so với S, tín hiệu ra D so với S.

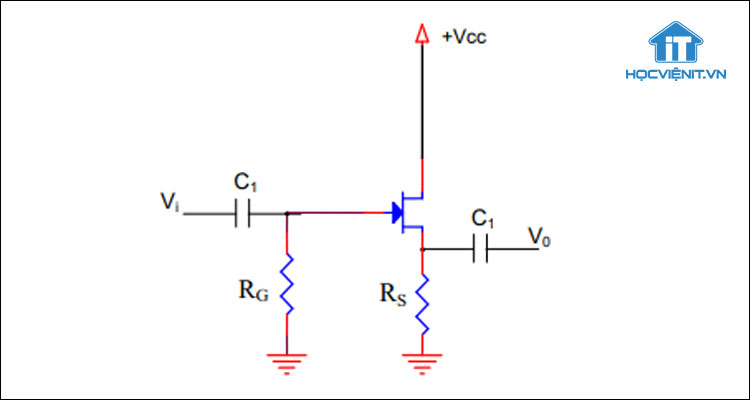

JFET mắc kiểu cực cổng chung (Common Gate = CG)

Tín hiệu vào S so với G, tín hiệu ra D so với G.

JFET mắc kiểu cực thoát chung (Common Drain = CD)

Tín hiệu vào G so với D, tín hiệu ra S so với D.

Trên đây là san sẻ của Học viện chuyên nghành iT.vn về JFET. Hy vọng những tri thức này còn có thể giúp ích cho bạn trong quá trình học tập và thao tác. Nếu có bất kì thắc mắc nào thì hãy để lại phản hồi ngay dưới nội dung bài viết này hoặc inbox trực tiếp cho HOCVIENiT.vn để được trả lời tốt nhất. Chúc bạn thành công!

Tìm hiểu thêm: Tổng hợp tri thức cơ bản về Transistor – Điện tử cơ bản

Mọi cụ thể chi tiết xin vui lòng liên hệ:CÔNG TY CỔ PHẦN HỌC VIỆN ITMST: 0108733789Tổng đài tương trợ: 024 3566 8686 – Hotline: 0981 223 001Facebook: www.fb.com/hocvienitĐăng ký kênh Youtube để theo dõi các bài học kinh nghiệm của Huấn luyện viên tốt nhất: http://bit.ly/Youtube_HOCVIENiTMạng lưới hệ thống cơ sở huấn luyện: https://hocvienit.vn/lien-he/Học viện chuyên nghành IT.vn – Truyền nghề thực tế cùng bạn đến thành công!